絕對(duì)值編碼器協(xié)議還挺多的,,比如常用德國(guó)公司的一些協(xié)議SSI,BISS,,ENDAT,,HIPERFACE協(xié)議等等,,還有日系的多摩川。當(dāng)然還有一些基于modbus的,,can的,模擬量的,。

絕對(duì)值編碼器的好處就在于,,編碼器掉電能保存編碼器的位置信息,重新上電后不會(huì)丟失,。不像光編編碼器,,上電無(wú)法知道絕對(duì)位置,需要找到z信號(hào),。不過(guò)絕編使用起來(lái)會(huì)相對(duì)麻煩點(diǎn),,需要通信協(xié)議,其成本也會(huì)貴一點(diǎn),。

它內(nèi)部的實(shí)現(xiàn)方式也有很多種,。感興趣的可以網(wǎng)上查一查。

SSI協(xié)議介紹

SSI通訊協(xié)議為縮寫(xiě),,其全稱為同步串行接口( Synchronous Serial interface ),,是一種廣泛使用的位置傳感器之間的串行接口和一個(gè)控制器。

SSI是RS-422上的單向串行協(xié)議,。單向時(shí)鐘由主頻產(chǎn)生,,并從80khz指定到2mhz。接收數(shù)據(jù)也是單向的,,SSI不支持傳播延遲補(bǔ)償,。

不活動(dòng)時(shí)時(shí)鐘為高電平。 為了啟動(dòng)數(shù)據(jù)傳輸,,時(shí)鐘變低并存儲(chǔ)位置,。在時(shí)鐘信號(hào)的第一個(gè)上升沿,MSB 在 SSI 編碼器處移出,。 在第二個(gè)上升沿,,MSB-1 被移出,,依此類推,直到最后一位 (LSB) 被移出,。 另一個(gè)時(shí)鐘周期后,,時(shí)鐘保持高電平,直到下一個(gè)數(shù)據(jù)傳輸開(kāi)始,。 根據(jù)超時(shí),,當(dāng)前鎖存位置或新位置值將在下一次傳輸中傳輸。

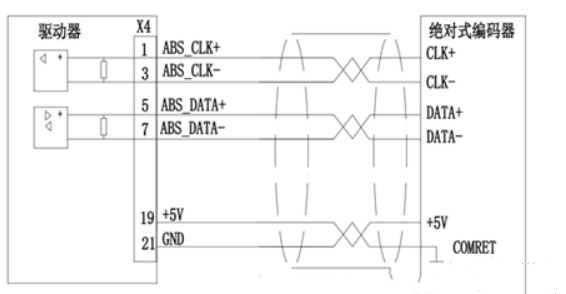

硬件接口

采用的是422的差分接口與絕對(duì)值編碼器連接,,一般SSI編碼器必須有6根線,,一般的編碼器可能是8根線(方向和置零)。

- 時(shí)鐘CLK+

- 時(shí)鐘CLK+

- 數(shù)據(jù)DATA+

- 數(shù)據(jù)DATA-

- GND

- VCC(5V-30V)

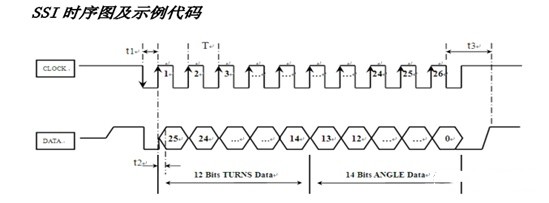

通信時(shí)序

隨便拿了個(gè)SSI編碼器的datasheet:

數(shù)據(jù)手冊(cè)上對(duì)時(shí)間的描述:

- t1>0.45us

- t2<0.40us

- t3=12us~30us

- T=1us~11us

協(xié)議特性

- 時(shí)鐘在80khz-2mhz

- 協(xié)議是單向的

- 空閑態(tài)時(shí)鐘為高

- 時(shí)鐘個(gè)數(shù)等于數(shù)據(jù)個(gè)數(shù)+1:第一個(gè)時(shí)鐘是觸發(fā)編碼器,,數(shù)據(jù)是從第二個(gè)時(shí)鐘開(kāi)始,。

- 時(shí)鐘上升沿觸發(fā)編碼器,下降沿鎖存數(shù)據(jù)

- SSI沒(méi)有傳播延遲檢測(cè)補(bǔ)償

- 一幀通信結(jié)束后,,需要空閑10-30us,。

驅(qū)動(dòng)器與編碼器通信

額外提一下,好一點(diǎn)的驅(qū)動(dòng)器架構(gòu),,都是雙核的,,一般都使用DSP+FPGA,或者是MCU+FPGA的方式.

為什么要使用FPGA,?

- 一部分原因就是因?yàn)樘幚砭幋a器的信號(hào),,通用驅(qū)動(dòng)器需要支持的編碼器協(xié)議有很多種,單個(gè)dsp或者mcu,,并不能都支持,。

MCU如何與SSI通信

IO模擬

如果自己想熟悉一下協(xié)議,做做測(cè)試,,可以用MCU的IO口模擬一下SSI協(xié)議,,讀取編碼器的信息。

SPI

一般使用MCU的SPI接口,。MCU作為Master主機(jī),,編碼器作為Slave從機(jī)。 SPI的CLK經(jīng)過(guò)差分電路后連接到編碼器的時(shí)鐘信號(hào)線上,。 SPI的MISO經(jīng)過(guò)差分電路后連接大編碼器的DATA信號(hào)線上,。

SPI有四種模式

SPI的相位(CPHA)和極性(CPOL)分別可以為0或1,組合構(gòu)成了SPI的4種模式(mode),。

時(shí)鐘極性CPOL: SPI空閑時(shí)鐘信號(hào)CLK的電平

- 1:高電平

- 0:低電平

時(shí)鐘相位CPHA: SPI在CLK哪個(gè)邊沿開(kāi)始采樣

- 0:第一個(gè)邊沿

- 1:第二個(gè)邊沿

| 模式 | 時(shí)鐘極性 | 相位 |

|---|---|---|

| 模式0 | CPOL=0(低電平) | CPHA=0(第一個(gè)邊沿:上升沿) |

| 模式1 | CPOL=0(低電平) | CPHA=1(第一個(gè)邊沿:下降沿) |

| 模式2 | CPOL=1(高電平) | CPHA=0(第一個(gè)邊沿:下升沿) |

| 模式3 | CPOL=1(高電平) | CPHA=1(第一個(gè)邊沿:上升沿) |

根據(jù)SSI的協(xié)議是時(shí)鐘空閑是高電平,,在下降沿采樣。所以我們需要把SPI配置成模式2,CPOL=1,,CPHA=0的模式,。

根據(jù)編碼器位數(shù),設(shè)置SPI的通信長(zhǎng)度,,通信后得到的數(shù)據(jù),,掐頭掐尾,丟掉第一個(gè)bit,,丟掉尾巴的多余的bit,。就得到了SSI的數(shù)據(jù)。

時(shí)序要求,,最后也要給編碼器一個(gè)空閑超時(shí)時(shí)間,,讓編碼器準(zhǔn)備下一次傳輸數(shù)據(jù)。 假設(shè)400k時(shí)鐘,,一個(gè)時(shí)鐘2.5us, 14位編碼器則需要15個(gè)時(shí)鐘*2.5us = 37.5us + 20us = 57.5us,。通信一次。

編碼器的多圈值和單圈值

什么是單圈編碼器,? 編碼器記錄的信息只記錄一圈內(nèi)的絕對(duì)位置,。

什么是多圈編碼器? 編碼器除了記錄一圈內(nèi)的位置信息,,還會(huì)記錄圈數(shù)。

SSI的數(shù)據(jù)格式

- 一般有二進(jìn)制格式,,以及格雷碼格式,。

- 二進(jìn)制,即是通信data,。

- 格雷碼,,是一種錯(cuò)誤最小化的編碼方式。需要解碼,,將格雷碼轉(zhuǎn)換成二進(jìn)制,。